Problem :- When a system uses several frequencies of clock oscillators in the same circuit to drive different

processors sequentially, several problems may be encountered.

In order to synchronize the discrete oscillators both frequency and time has to be taken into account.

It is important to ensure that the start-up time for all of the oscillators is consistently the same

without any hysteresis.

If the time taken to reach the frequency of oscillation required differs from the gate speed of the

processor then a sequencing error will occur.

This may require an additional synchronizing circuit to control the start up with relation to the

gate speed.

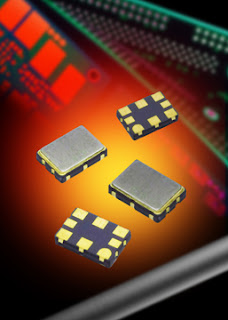

Solution:- The QuikXO HC_JF low phase jitter series of selectable quad output oscillators has been

designed for this type of application. The oscillator offers 4 user selectable outputs in a choice of

LVCMOS, LVPECL, LVDS, CML and HCSL outputs, in one package ensuring that the synchronization problem

is eradicated.

No comments:

Post a Comment